Vp suppression algorithm

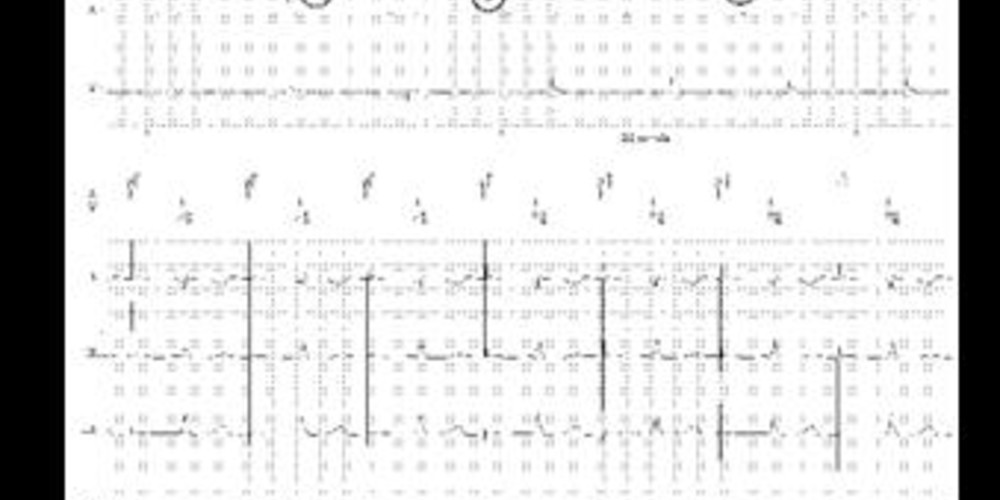

Tracing

Manufacturer Biotronik

Device PM

Field Pacing Modes

N° 7

Patient

Same patient as in tracing 1.

Graph and trace

Programming in DDD mode 60 beats/minute followed by programming of the Vp suppression algorithm;

- atrial pacing and ventricular pacing (AP-VP); DDD mode 60 bpm;

- programming of the Vp suppression algorithm (ADI-DDD mode);

- atrial pacing and spontaneous ventricular event (long PR pattern).

Other articles that may be of interest to you

There is vast body of literature demonstrating the deleterious effect of prolonged right ventricular pacing. Concomitantly, any reduction in unnecessary ventricular pacing allows battery saving and prolongs the life of the pacemaker. Various modes have been proposed by device manufacturers to reduce the percentage of ventricular pacing without compromising the safety of the patient during the occurrence of an atrioventricular conduction disorder. The preferred indication of this type of mode is therefore the presence of sinus dysfunction with an atrioventricular conduction that is either preserved or altered in a paroxysmal manner. On this tracing, the programming of the ADI-DDD mode can significantly reduce the percentage of pacing pulses compared to permanent DDD mode pacing. In the long term, this should prove beneficial in terms of ventricular remodeling and occurrence of atrial arrhythmia. Analysis of the percentage of ventricular pacing is therefore an important follow-up component in a patient with sinus dysfunction, with the aim of reducing to a minimum the occurrence of any unnecessary ventricular pacing.

When the Vp suppression algorithm is programmed, the pacemaker operates in ADI(R) mode and switches to the DDD(R) pacing mode if atrioventricular conduction is impaired. It should be noted that on this tracing, the PR interval is relatively prolonged (around 400 ms on paced P wave). There is a switching criterion for first-degree AV blocks. The PR interval due to spontaneous or paced atrial activity must exceed 450 ms over 2 consecutive cycles (non-programmable value), which is not the case in this instance.